所謂的影響性能是并不是指SDRAM的帶寬,頻率與位寬固定后,帶寬也就不可更改了。但這是理想的情況,在內(nèi)存的工作周期內(nèi),不可能總處于數(shù)據(jù)傳輸?shù)臓顟B(tài),因?yàn)橐忻睢ぶ返缺匾倪^程。但這些操作占用的時間越短,內(nèi)存工作的效率越高,性能也就越好。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605998 -

SDRAM

+關(guān)注

關(guān)注

7文章

430瀏覽量

55367 -

時序

+關(guān)注

關(guān)注

5文章

392瀏覽量

37428

發(fā)布評論請先 登錄

相關(guān)推薦

SDRAM的基礎(chǔ)知識和操作時序

是怎么來把這篇文章中的這些操作用代碼寫出來。參考書籍:1.《高手進(jìn)階 終極內(nèi)存技術(shù)指南》2. 廠商官方手冊轉(zhuǎn)載請注明:鄧堪文博客 ? SDRAM理論篇之基礎(chǔ)知識及

發(fā)表于 01-24 06:35

SDRAM的原理和時序

SDRAM的原理和時序

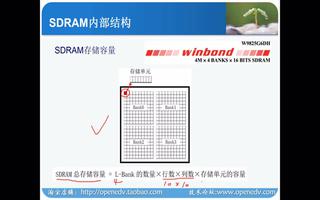

SDRAM內(nèi)存模組與基本結(jié)構(gòu) 我們平時看到的SDRAM都是以模組形式出現(xiàn),為什么要做成這種形式呢?這首先要接觸到兩個概念:物理Bank與芯片位寬

發(fā)表于 03-11 14:43

?167次下載

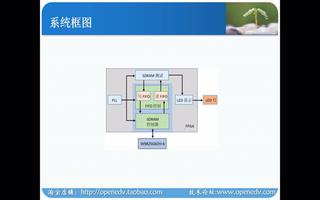

FPGA讀寫SDRAM的實(shí)例和SDRAM的相關(guān)文章及一些SDRAM控制器設(shè)計(jì)論文

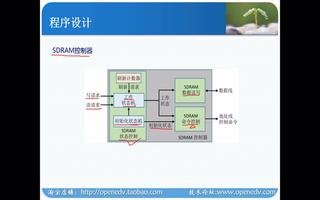

,SDRAM的原理和時序,SDRAM控制器,動態(tài)隨即存儲器SDRAM模塊功能簡介,基于FPGA的SDRA

發(fā)表于 12-25 08:00

?56次下載

正點(diǎn)原子開拓者FPGA:SDRAM時序操作(2)

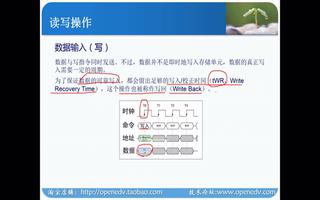

通常DRAM是有一個異步接口的,這樣它可以隨時響應(yīng)控制輸入的變化。而SDRAM有一個同步接口,在響應(yīng)控制輸入前會等待一個時鐘信號,這樣就能和計(jì)算機(jī)的系統(tǒng)總線同步。

正點(diǎn)原子開拓者FPGA:SDRAM讀寫測試實(shí)驗(yàn)(2)

SDRAM從發(fā)展到現(xiàn)在已經(jīng)經(jīng)歷了五代,分別是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3

正點(diǎn)原子FPGA之SDRAM:SDRAM操作時序(2)

正點(diǎn)原子FPGA之SDRAM:SDRAM操作時序(2)

評論