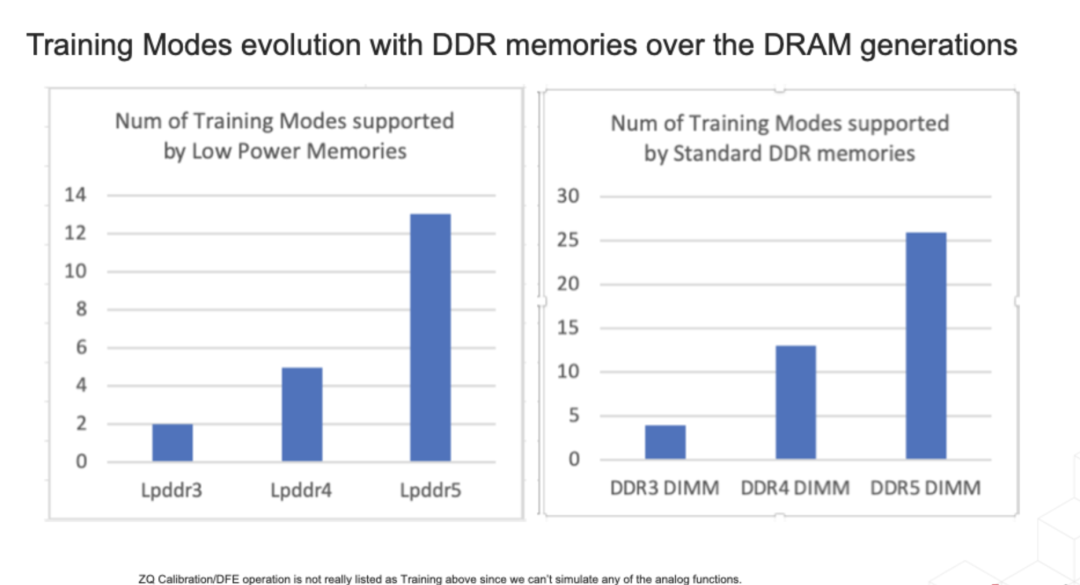

隨著每一代接口(Interface)和存儲(memory)的頻率和速率的提高,信號采樣以及傳輸變得越來越困難,因為數據眼(data eyes)越來越小。

為了幫助高速 I/O 握手,接口和存儲支持越來越多的Training Modes,系統設計人員必須將這些Training Modes作為系統bring up和正常操作的一部分,以使系統能夠按預期工作。

尤其是對于數據中心業務,這些training mode非常重要。

以下是 LPDDR5/DDR5 DIMM 等最新 DRAM 支持的最重要的training mode:

1.Vref Training

這是內存子系統初始bring up的部分。Host通常會設置 DRAM 模式寄存器,該寄存器將用作command、chip select和 DQ 等信號的參考電壓。由于DRAM 可能無法在完成 Vref training之前對 Host 命令進行采樣,因此 Host 會分多個周期發送該命令,以確保 DRAM 能夠接收該命令。

2. Command Training

這通常是Host必須執行的第一個功能Training,以確保 DRAM 設備能夠理解它發送的命令。它涉及Host驅動 DRAM 的command總線,然后DRAM對 DQ 信號進行采樣并反饋回去。Host可以檢查反饋并與它驅動的內容進行比較。如果反饋與驅動的內容不匹配,Host可以調整輸入。

3. Clock to Strobe leveling

由于布線差異等其他因素,DRAM 使用的strobe信號通常不會與它接收的輸入時鐘對齊。Host必須通過Clock to Strobe leveling來調整此相位差。此training稱為 DDR5 的Write leveling。

4. Strobe to DQ Training

完成 Clock to Strobe training后,下一步是確保 Host 和 DRAM 能夠正確發送/采樣寫入和讀取數據。這一步的目的是讓 Host 知道strobe和data信號的時序關系,稱為Strobe to DQ training。它通常涉及寫入 DRAM 已知數據,然后從同一位置讀取并比較兩者以檢查它們是否匹配。然后,Host將其調整strobe和data的相位關系,并再次執行相同的步驟,直到它能夠正確地向 DRAM 寫入/讀取數據。

5. Other Trainings

通常在DIMM中還支持其他幾項trainings,以幫助實現設備的特定調整。對于 DDR5 DIMM 等設備,trainings不僅涉及單個組件(RCD、DRAM、DB),還涉及信號如何從一個組件傳播到另一個組件。Host需要training單個組件以及整個模塊,例如一些 DDR5 LRDIMM模塊級trainings的示例(如 MRE、MRD、DWL、MWD 等)。

總之,trainings是接口和存儲系統啟動和正常功能的重要組成部分。它也日益成為一個重要的設計和驗證挑戰,需要作為 SOC 規劃的一部分加以考慮。

審核編輯:湯梓紅

-

DRAM

+關注

關注

40文章

2326瀏覽量

183868 -

寄存器

+關注

關注

31文章

5363瀏覽量

121194 -

接口

+關注

關注

33文章

8694瀏覽量

151928

原文標題:高速DRAM的training

文章出處:【微信號:數字芯片實驗室,微信公眾號:數字芯片實驗室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高速DRAM的training

高速DRAM的training

評論