本文用的芯片型號為xcku115-flvd1924-1L-i,時鐘頻率為400MHz。

兩個有符號數相加

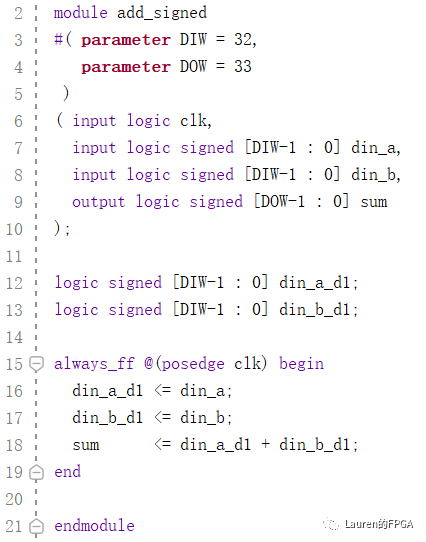

采用RTL代碼描述位寬相同的兩個數相加或相減,無論是有符號數還是無符號數,Vivado綜合后的結果是一致的。以32bit數據為例,相應的代碼如下圖所示。這里考慮到兩個32bit數據相加其結果可能為33bit,同時對于高速設計(時鐘頻率至少400MHz)為了滿足性能,對輸入和輸出分別添加了流水寄存器。

最終的資源利用率如下圖所示。

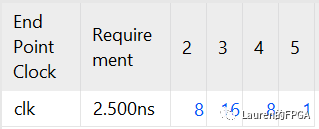

從邏輯級數的角度看,邏輯級數最大為5(有一條),大多數路徑為3,如下圖所示。

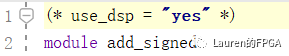

從綜合屬性角度看,可以通過use_dsp屬性使得該加法操作映射到DSP48中,該屬性的使用方法如下圖所示。

采用DSP48實現時,上述代碼可達到完全映射,不會消耗SLICE中的任何資源。假定時鐘頻率為400MHz,對比使用LUT+FF和DSP48兩種實現方式,不難看出后者在時序(邏輯級數降低至1)和功耗方面均有優勢。

-

寄存器

+關注

關注

31文章

5363瀏覽量

121169 -

RTL

+關注

關注

1文章

385瀏覽量

59950 -

代碼

+關注

關注

30文章

4827瀏覽量

69054

原文標題:兩個數相加,三個數相加有什么不同

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何把兩個數據返回給調用函數

ADS125H01測量結果在兩個數值之間跳變,如何規避此類問題?

邏輯異或和邏輯或的比較分析

實現兩個單一頻率正弦波相加的加法器的芯片選取有什么特殊要求嗎?opa2320可以嗎?

如何使用SPI或UART連接兩個ESP模塊?

同相加法器和反相加法器的區別是什么

相同的代碼,不同的工程出現定時器搶占的現象怎么解決?

用STM32F1xxx來同時對TIMR4的兩個輸入脈沖進行脈寬測量,脈沖要如何計算?

傳感器之外—兩個數據庫之間的“連接”查詢

采用RTL代碼描述位寬相同的兩個數相加或相減

采用RTL代碼描述位寬相同的兩個數相加或相減

評論